# コグニティブ RF および EW システムの組込みテクノロジ

### はじめに:

なりすましネットワークの犠牲になることなく空港で Wi-Fi を見つけようとするビジネス旅行者のように些細なことであろうと、混雑した環境で位置データを送信しようとする戦闘機のように重要なことであろうと、敵対的な地域での電磁スペクトルはますます重要になっています。これらの新しい方法論は、コグニティブ RF およびコグニティブ EW と呼ばれることが多く、ミッション中にフィールド内の新しい脅威を検出、学習、および適応できる再構成可能なハードウェアとソフトウェアに依存しています。

多くのビジネス旅行者にとって、彼らの携帯電話には利用可能な周波数帯に基づいて信号品質を改善するための多くの技術が含まれていますが、旅行者は過去の経験に基づいて独自の手法を開発しています。これらのいくつかは環境に依存します(カフェ:そこには良好な Wi-Fi 環境があります)。一部は経験に基づいています(「Jim's big phone」と呼ばれるホットスポットに接続しない事)。また、その場で判断する必要があるものもあります(例えばホテルのホットスポットのように見えますが、ログインページがおかしいものがあります。これは念のため使用しない事)。これらの旅行者が本質的に行っているのは、感覚、学習、適応のプロセスです。これは、コグニティブ RF とコグニ

# スピードの必要性:

ティブ EW に関する現在の研究の中心にあるものです。

固定アナログシステムから完全にデジタルプログラム可能なシステムへのレーダーおよび EW システムの動きの増加により、周波数可変能力または高度な変調技術を使用して動作周波数範囲を拡大することが可能になりました。レーダーシステムの場合、これらの手法は検出が困難であるだけでなく妨害やなりすましも困難であることを意味します。これにより、レーダーシステムの妨害やなりすましが困難になります。

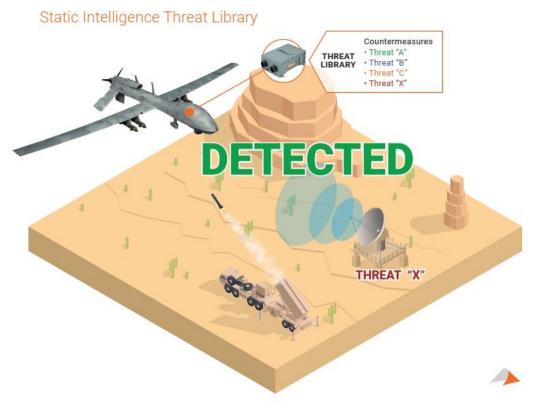

レーダーは周波数可変能力「ホッピング」信号や低被探知(LPI)技術など、より広い帯域幅を活用するため、妨害および干渉技術も動作周波数範囲を拡大する必要があります。最終的な結果は、処理能力と帯域幅の拡大競争となりこれはますますペースが速くなっています。従来、レーダーおよび EW システムは、静的脅威ライブラリに対応して開発された対策を展開していました。この運用モードは、システムは既知の脅威に対抗するように設計され徹底的にテストされました。

MISH

未知の脅威が検出された場合、いくつかの一般的な対策が採用された可能性がありますが、一般的にミッション後の分析のために新しい脅威に関する情報が収集されます。その後、実験室でさらに分析が行われ静的脅威ライブラリの更新がテストされ発行されます。このプロセスには数ヵ月、場合によっては数年かかる場合があります。脅威のアップグレードプロセスが同様のスケジュールに従った場合、この方法で問題ありませんでした。

### 柔軟性と適応性の必要性:

もう1つの新たな問題はこれらの新しい対策の実施です。古いシステムはアップグレードが難しく、システムのメモリ (ROM)を取り外して交換する必要がある場合があります。最新のシステムは、安全なコンピュータをプラットフォーム上のポートに接続することで、運用中の戦場で脅威ライブラリを更新できるように進化しました。将来の機能では、これらの脅威ライブラリを文字通りオンザフライで更新する機能を想定しています。

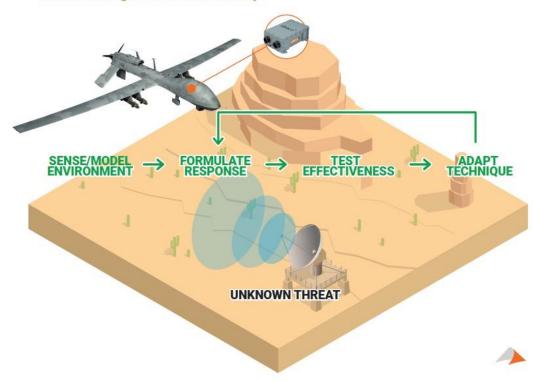

これらの新しい方法論は、コグニティブ RF およびコグニティブ EW と呼ばれることが多く、ミッション中にフィール ド内の新しい脅威を検出、学習、適応できる再構成可能なハードウェアとソフトウェアに依存しています。これを可能 にするために、脅威ライブラリの学習と適応のプロセスがフィードバックループになり、新しい対策をその場で開発で きるようになります。これには、処理性能の大幅な飛躍が必要です。これは、サイズ、重量、電力を大幅に増加させる ことなく達成する必要があります。この新しい方法論は、戦術的エッジでコグニティブおよび機械学習 EW システムと 呼ばれます。

# Countermeasures THREAT THREAT

# 再構成可能なハードウェア:

EW システムでの認識が必要なのは、現実世界の紛争中に敵のミサイル火器管制レーダーなどの従来の静的な脅威が、これまで遭遇したことのない新しい未知のモードに切り替わり、その結果脅威ライブラリに対抗策がないことが想定されるためです。言い換えれば、新しい EW システムは未知の脅威を検出して対抗できる必要があります。

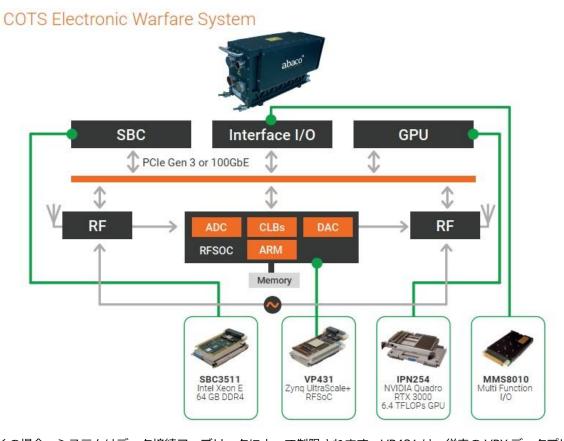

これには大量のコンピューティングリソースが必要であり、ヘテロジニアスシステムは3つの主要なコンピューティング要素(FPGA、GPGPU、ホストベースのCPU)を使用して必要なリソースに対応します。各計算要素はそれぞれ補完的な機能を提供します。FPGAは、エネルギー検出やデジタルダウンコンバージョンなどの高帯域幅、低遅延のフロントエンド RF 処理タスクに優れています。FPGAは、広帯域レシーバに関連する非常に高いデータレートを処理したり、デジタルビームフォーミングやヌルステアリングを実行するためにそのようなデータストリームを処理したりするのにも理想的です。最新のモジュラーアーキテクチャは、バックプレーンデータトランスポートとスイッチも提供し、100Gb/sを超える速度でこれらのコンピューティング要素間で大量のデータをリアルタイムで移動します。FGPAは、固定小数点処理にも優れています。

一方 GPGPU は、OpenCL, CUDA, Halide などの従来のプログラミング言語で開発できる複雑な人工知能(AI)および機械学習(ML)アルゴリズムに柔軟性を提供する、大量の並列処理浮動小数点計算要素を提供します。最後に、高性能マルチコア CPU により C#や Python などの言語を使用して、豊富なフローティングポイント環境で処理されたデータを継続的に改良できるだけでなく、通信、システムセキュリティ、オペレーターインターフェイス、データストレージを提供できます。

計算要素の異なる開発環境やソフトウェアモジュールレベルのインターフェイスを標準化する必要性など、システムの 実装には課題が残っています。計算要素間でデータを移動するタスクを容易にすることを約束する最近の開発は、

Photon イニシアチブです。Photon は MITRE Corporation によって開発され、CPU と GPGPU ベースの信号プロセッサの両方にデジタル信号情報を効率的に配信できるフレームワークであり、すべての EW ベースのソリューションの開発全体で一貫性を確保するために米国陸軍に採用されました。

Photon は、モジュール式で再利用可能な AI/ML 機能を戦術レベルでの実装を可能にするものであり、複数のストーブパイプ処理フレームワークと検出器を単一のプラットフォームに統合します。Photon は、SIGINT、EW、Cyber の機能を統合するための最新の基盤を提供します。VITA 66.4 などの VPX バックプレーンの光拡張は、追加のボード間通信のための追加のプロトコルに依存しない高速光レーンを提供します。3U VPX は、電力、サイズ、重量あたりの高い処理能力を提供し、統合ソリューションはあらゆる環境に合わせて調整できます。さらに、OpenVPX(VITA 65)、VPX(VITA 46.0)、FMC(VITA 57.1)、FMC+(VITA 57.4)などの規格ベースのインターフェイスを使用することで将来のハードウェアのアップグレードが容易になります。

### 低レイテンシの処理能力:

これまで見てきたように、コグニティブシステムには複数のチャネルと広い RF 帯域幅が必要です。つまり、処理する必要のあるデータスループットは膨大です。ただし、処理アーキテクチャは、最新の RF および EW システムで克服する必要のある技術的課題の 1 つにすぎません。

このセクションでは、データをできるだけ迅速に移動および処理する必要があり、入力と出力間のバッファリングまた は遅延を最小限に抑える必要があるため、エンドツーエンドのシステム遅延について検討します。

この種のシステムは従来、デジタル RF メモリ(DRFM)と呼ばれていました。DRFM システムは、発信者が DRFM の影響を検出しないようにする時間枠内で、RF 脅威に対抗するように設計された低遅延の閉ループ脅威/応答システムです。DRFM の最も一般的なアプリケーションは、レーダー信号の妨害となりすましです。これはたとえば、ターゲットの自然な署名に関して受信者を欺いたり、誤ったターゲットを作成したりするために使用できます。DRFM の重要な機能はコヒーレンス(同位相)であり、これはソース送信とコヒーレント(同位相)であることを意味します。つまり、RF 入力(検出)から RF 出力(効果)までの遅延が非常に短いことを意味します。

FPGA は、低遅延で高速データの一定のストリームを処理できるため、コグニティブシステムの主要なテクノロジ要素です。コグニティブレーダーと EW 技術が開発されるにつれて、重要なフロントエンド処理リソースの需要が劇的に増加しています。コグニティブシステムは適応型ビームフォーミングとフェーズドアレイを活用することが多いため、信号処理の負荷はフロントエンドに向かってますます進んでいます。高度に並列化された操作でストリームベースの処理を実行する優れた機能により、高性能 FPGA を導入してデータ取得と信号処理を実行すると、消費電力と遅延を削減しながらパフォーマンスを大幅に向上させることができます。これにより、決定されていないタスクがシステムのバックエンドの CPU または GPU に委ねられます。

### Static Intelligence Threat Library

# 革新的なテクノロジ:

前述したように、帯域幅の拡大競争は RF および EW システム開発の重要な要素であり、アナログ RF パフォーマンスが重要です。この課題を克服するために、Abaco Systems は、必要なデータをデジタル化し FPGA にできるだけ早く取り込むための 2 つの異なるアプローチを提供しています。多くの場合、業界をリードする FMC および FMC+ (VITA57.1 および VITA57.4) ポートフォリオの高性能アナログ-デジタル変換モジュールを利用しています。FMC+を使用すると、Virtex UltraScale+ FPGA、Zynq UltraScale+ MPSoC、

および FMC+サイトを備えた VP889 などの最新の 3U VPX FPGA キャリアの高速トランシーバーに直接低遅延インターフェイスを採用するモジュラーAD/DA ボードを使用できます。FMC+などのメザニン規格を使用すると、ADCカードを簡単にアップグレードできるため、Texas Instruments などの企業の最新の高速 ADC テクノロジで直接 RFサンプリングを行うことができます。

新しいアプローチは、マルチギガサンプルの ADC と DAC を SoC アーキテクチャに統合した最初の FPGA プロセッサ

MISH

であるザイリンクスの革新的な RF システムオンチップ(RFSoC)テクノロジを活用することです。Zynq UltraScale+ RFSoC は、統合された ADC、DAC、構成可能なロジックエレメント、マルチプロセッサ組み込み Arm Cortex-A53 アプリケーション処理ユニット(APU)、および ARM リアルタイム処理ユニット(RPU)を備えています。これにより、RF 信号チェーンの複雑さを軽減しながら入力/出力チャネル密度を最大化できます。この利点は、システム遅延の削減とチャネル密度と信号処理機能の理想的なバランスです。

例として、Abaco VP431 3U VPX RFSoC ボードは、4.0~5.0GSPS の統合 8 チャネル 14 ビット ADC サンプリング と、6.4~10GSPS の統合 8 チャネル 14 ビット DAC サンプリングを備えています。この簡素化によりシステムの待ち 時間が短縮され、ユーザーは FPGA のプログラマブルロジックを活用して、コグニティブ対策に不可欠な他のタスクを 実行できます。

# Cognitive EW Computing Requirements

さらに、VP431のヘテロジニアス処理機能により組み込み ARM Cortex プロセッサを意思決定および制御プロセスに利用できるようになり、GPGPU または CPU あるいは一部のアプリケーションの効率が最適化され、プロセッサを追加する必要が完全になくなります。追加の処理が必要な場合、システム開発者はシステムに高データレートの複数のチャ

General Purpose Processor (GPP)

Deep Learning Algorithms

Graphics Processors (GPU)

ネルが含まれている場合に生成される膨大な量のデータを処理する方法に課題があります。

多くの場合、システムはデータ接続ファブリックによって制限されます。VP431 は、従来の VPX データプレーンインターフェイスを備えており、ホストコンピューターへの x4 PCIe Gen3 接続を可能にします。1 サンプルあたり 2 バイトで 5GSPS を超えるレートでサンプリングする 8 つの ADC では、最新の PCIe Gen3 高速データ接続でさえこの速度でのデータ転送に対応できません。

この課題を克服するために、VP431 には、PCIe Gen3 データプレーンに加えて、2x 100Gb/s リンクを可能にする 8 チャネル VITA 66.4 光ファイバーリンクオプションが含まれています。以前のテクノロジでは、同じレベルのパフォーマンスと統合を実現するために 4 倍のボードが必要でした。

EW UAS における無人航空機システム(UAS)の役割の増大は、スタンドインおよびスタンドオフの妨害とインテリジェンス監視および偵察(ISR)ミッションの両方にとって理想的なプラットフォームです。UAS は、同様のサイズの有人プラットフォームと比較した場合、より大きなペイロードを運ぶことができます。

しかしさらに重要なことに、それは潜在的に致命的な状況に乗組員を置くことなく、より低い運用コストで危険または 困難なタスクを安全かつ効率的に実行することを可能にします。多くの UAS の課題は、多くの小さな UAS のペイロードが減少するため、EW システムのサイズ、重量、電力(SWaP)を削減することです。これは、Sensor Open Systems Architecture(SOSA)標準のような費用効果の高い業界標準の使用の背後にある推進力の影響です。SOSA標準に準拠した 3U VPX システムは、高帯域幅のヘテロジニアスコンピューティング環境における SWaP の課題に対処できます。

進化する UAV EW プログラムの例は、米陸軍の多機能電子戦-エアラージ(MFEW-AL)です。MFEW-AL は、MQ-1C グレイイーグル UAS に搭載されたエアボーン EW ポッドを使用します。グレイイーグルは、由緒ある General Atmics 製 MQ-1B プレデターUAS の最新バージョンです。MFEW-AL はコマンダーに 2 つの新機能を提供します。1 つは有機的な電子攻撃および妨害機能であり、もう一つは電磁検知および収集機能を提供する電子サポートです。MFEW-AL には、攻撃的な電磁サイバー攻撃を実施するための要件が含まれています。

# まとめ:

コグニティブ処理とより多くの帯域幅の絶え間ない必要性は、レーダーと EW 処理サブシステムのパフォーマンス要件を大幅に押し上げていますが、サイズ、重量、および電力の可用性は低下しています。

これらの要件は、マルチコアプロセッサ、GPU、ザイリンクスの RFSoC および Zynq MPSoC FPGA などの高度なテクノロジを使用することで正常に対処できるため、開発者は適切な認知およびデジタル処理アルゴリズムのレーダープロトタイピングに集中できます。

次世代のコグニティブレーダーおよび EW システムの場合、VP431 および同様の製品は、エンドツーエンドの遅延とシステムパフォーマンスにおいて、敵に対して必要な優位性を提供できます。

### Abaco Systems 社について

Abaco Systems 社は、30 年以上前の英国 Plessey Microsystems 社がルーツとなる企業です。Plessey 社は ICS 社と Octec 社を買収して Radstone 社となりました。2006 年に Radstone 社は、SBS 社、VMIC 社、Condor 社などの組 み込みコンピューティング企業を買収した GE Fanuc Embedded Systems 社に買収されました。2015 年に Embedded Computing 部門が Veritas Capital 社に買収され、Abaco Systems 社が誕生しました。更に Abaco Systems 社は 4DSP 社を買収し、FPGA ボードや AD/DA FMC モジュールのラインナップを拡充して組み込みシステム ビジネスのリーダーとしてマーケットを牽引しています。Abaco Systems 社の詳細については、www.abaco.com を 参照してください。